## Effect of Modulation Index on Switched Capacitor Based Inverter using PDD PWM

Bhagyalakshmi P S<sup>1</sup>, Beena M Varghese<sup>2</sup>, Dr. Bos Mathew Jos<sup>3</sup>

Student<sup>1</sup>, Professor<sup>23</sup>

Mar Athanasius College of Engineering, Kothamangalam, Kerala, India<sup>123</sup>

Abstract- Power electronics semiconductor devices that are produces a sinusoidal voltage on many levels is called a multilevel inverter. They generate output that is more pristine and has lower harmonic distortion. The number of Switched Capacitor (SC) cells in this architecture determines the number of output levels, based on switched capacitor technology. By adjusting the capacitors in series and parallel, a lower voltage can be converted to a higher output. The circuit employs fewer components than a conventional switched capacitor multilevel inverter with the same architecture. Using Phase Delayed Disposition (PDD) PWM, inverter switching pulses are produced. Effect of frequency and amplitude modulation index are also examined in this paper in PWM techniques. At different modulation indices, the output voltage, Crest Factor, and %THD are assessed. The software used for the simulations is SIMULINK/MATLAB. The control mechanism is a crucial part of the circuit and is employed in conjunction with the PIC16F877A microcontroller to generate switching signals.

Keywords— Switched capacitor, single DC source, charging pump, and multilevel inverter

## I. INTRODUCTION

Electric cars, distributed generation, electrical energy systems, and renewable energy sources like fuel cells and photovoltaic have all become increasingly important in the fight against environmental problems worldwide in recent years. In addition, it is expected that the power electronic equipment required for these systems-converters, inverters, etc.-would be able to manage bigger voltage and capacity ratings given the rate at which electrotechnic sectors are evolving. Multilevel inverters are one solution to this problem, because of their benefits in high power with low harmonic applications.

In contrast to a two-level inverter, a multilayer inverter produces an output phase voltage that is stepped and has a more complex harmonic profile [1]. Multilayer inverters perform power conversion in several voltage stages in order to provide higher voltage capability, improved electromagnetic compatibility, decreased switching losses, and superior power quality. Multilevel voltage source inverters come in three commercial topologies these days; the diode-clamped, flying capacitor, and cascaded H-bridge [1] designs are the most often used. Certain topologies, such as cascading H-bridges, employ several sources in order to achieve increased output levels. The challenge with diode clamped or neutral point clamped is that as the level rises, there are more clamping diodes. Similar to this, the flying capacitor multilayer inverter system gets larger as the number of capacitors grows. The cascaded H bridge inverter achieves the highest output voltage and power levels among these inverter topologies. The source voltage alone will be the output's highest amplitude value in each of the aforementioned topologies, with the remaining levels representing only a small portion of the input voltage.

A packed U-cell (PUC) inverter may output seven different voltage levels using 6 switches, single DC voltage source, and a capacitor whose voltage needs to be adjusted to fix at one-third of the first DC source [25]. The aforementioned topology requires less components than other topologies of seven level inverter [25]. The maximum output voltage level is the same as the input DC voltage alone.

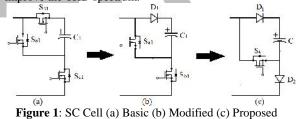

Under typical circumstances, output voltage of the inverter is equals to its input voltage when the unity modulation index. A boost converter is used to raise the output levels, guaranteeing a larger load voltage [3]. As an alternative, we can employ inductors or transformers at the output side. A charge pump produces a voltage which is more than the input voltage by using switched capacitors [3]–[5]. The charge pump adds the one voltages over the input voltage sources and the capacitors [20]. A SC inverter produces multilayer voltage outputs by using switched capacitors. A charge pump and a SC inverter are similar in terms of topology. Figure 1 shows how a standard switched capacitor (SC) cell is converted into a suggested SCMLI. A standard SC cell includes three switching devices plus one capacitor; a modified SC cell has two switching devices, one diode, and one capacitor. Based on the Basic and Modified Inverter topologies, a new SC based Inverter is proposed. Proposed MLI is derived [3]-[10] to reduce the number of components and improve the THD spectrum.

Multicarrier Pulse Width Modulation is the primary method used to regulate multilevel inverter switches, and it can be used to lower the harmonic contents [6]. In order to generate switching pulses, Sinusoidal Pulse Width Modulation compares triangular carrier signals with sinusoidal modulating signals. The modulating signal's amplitude determines the PWM modulation index. The impact of varied modulation index on the maximum output voltage and the inverter's THD spectrum is examined.

## **II. SEVEN LEVEL INVERTER**

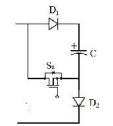

A full bridge inverter and a SC network are the two structures that cascade to generate this high level switched-capacitor (SC) multilevel inverter [6]-8]. The fundamental switching capacitor cell, as described in [10], is depicted in figure 2 and determines the level number at the load terminal. The primary benefit of this circuit is its extremely minimum switches in compared to other traditional topologies.

Figure 2: Basic Switched Capacitor Cell [10]

A cascade of N switched capacitor cells can create (2N+3) levels with a highest level of (N+1)V<sub>dc</sub>. A basic SC cell having a capacitor, a switch, and 2 diodes, as shown in figure 2. Each block is designed for a parallel and series connection by properly switching the common switch S<sub>b</sub> and the switch S<sub>a</sub>. The forward biased diodes establish a parallel connection between the input and capacitor. An input source is in series with a SC capacitor when switch Sa is turned ON. These devices need to be switched correctly in order to receive the desired output.

Figure 2: Circuit diagram of Seven Level Inverter

In this work, two switched capacitor cells are used to analyse a seven-level inverter. Every switched capacitor cell is connected to the voltage source through a switch S<sub>b</sub>, as illustrated in Figure 3 and described in [10].With the elimination of the switched capacitor network, the aforementioned circuit operates as a standard H-bridge inverter, producing three output levels, the highest of which is the input DC voltage (V<sub>dc</sub>). Two additional levels are produced in each half cycle and a maximum output level of 2V<sub>dc</sub> is obtained by adding one switched capacitor module or cell with  $V_{dc}$  as the capacitor voltage.

Number of levels at output = 2N+3(1)Where N is the number of SC Module

## **III. WORKING MODES OF SEVEN LEVEL INVERTER**

The multilevel inverter with switched capacitors that can generate up to seven levels is examined in this article; the circuit should use N=2 capacitor cells. When the capacitors are connected in parallel to the input voltage source, they start to accumulate charge. When the capacitors are connected in series with the input voltage source, they discharge [10]. The output of the switched capacitor network serves as the input for the single phase inverter.

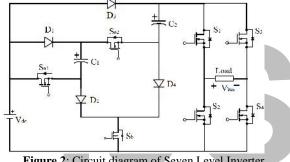

## A. Mode 1 ( $V_{bus} = 0 V$ )

All capacitors are generated in parallel with the input voltage source by turning on the switch Sb, which keeps an input voltage across each capacitor. Switches in the same upper/lower limb conduct to produce the zero voltage at the output shown in figure 4 when S2 and S4 or S1 and S3 are turned ON.

## B. Mode 2 $(V_{bus} = V_{dc} - V_f)$

As shown in figure 5, where Vf is the forward voltage drop of diode D3, the first level, which is equal to (Vdc -Vf), is produced in this mode by turning on the full bridge inverter's switches S1 and S4. Additionally, turn on Switch SB so that the capacitor can be charged.

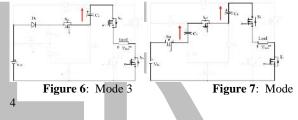

## C. Mode 3 ( $V_{bus} = V_{dc} + V_{C2} - V_f$ )

When one capacitor is linked in series, this is the mode. Figure 6's switch Sa2 is simultaneously turned ON to connect the capacitor C2 in series with the source. During this time, the complete bridge inverter's switches S1 and S4 are conducting. Vdc + VC2 - Vf is the output voltage as a result. where VC2 is the voltage of capacitor C2 and Vf is the forward voltage drop of diode D1.

## D. Mode 4 ( $V_{bus} = V_{dc} + V_{C1} + V_{C2}$ )

The two capacitors are connected in series in this manner. As seen in figure 7, the capacitors C1 and C2 are linked in series with the source voltage by connecting the switches Sa1 and Sa2. During this time, the complete bridge inverter's switches S1 and S4 are operating. The voltage level that is left is  $(V_{dc} + V_{C1} + V_{C2})$ , where  $V_{C1}$  represents capacitor C<sub>1</sub>'s voltage and V<sub>C2</sub> represents capacitor C<sub>2</sub>'s voltage.

As with S1 and S4, S2 and S3 can be set ON to produce the negative half cycle or OFF to provide the seven level output. Within the switched capacitor network, the input voltage determines the maximum voltage stress across each switch.

| LEVELS                               | S <sub>1</sub> | S2 | S <sub>3</sub> | $S_4$ | Sai | Sat | Sh |

|--------------------------------------|----------------|----|----------------|-------|-----|-----|----|

| 0                                    | 0              | 1  | 0              | 1     | 0   | 0   | 1  |

| $V_{de}$ - $V_{f}$                   | 1              | 0  | 0              | 1     | 0   | 0   | 1  |

| $V_{de} + V_{C2} - V_f$              | 1              | U  | U              | 1     | 0   | 1   | 0  |

| $V_{de} + V_{C1} + V_{C2}$           | 1              | 0  | 0              | 1     | 1   | 1   | 0  |

| - (V <sub>de</sub> -V <sub>f</sub> ) | 0              | 1  | 1              | O     | 0   | 0   | 1  |

| - ( $V_{dk} = V_{C2} - V_f$ )        | 0              | 1  | 1              | 0     | 0   | 1   | 0  |

| - $(V_{de} - V_{C1} + V_{C2})$       | 0              | 1  | 1              | o     | 1   | 1   | 0  |

Table 1: Switching Sequences of Seven Level Inverter

The switching pattern displayed in Table 1 can be used to demonstrate how the above topology operates in detail. The switches for each level in this table have values of 0 or 1, meaning that a switch with a value of 1 is in the ON state and a switch with a value of 0 is in the OFF state.

## **IV. PULSE WIDTH MODULATION SCHEMES**

An effective modulation method is needed to regulate and generate an output waveform of good quality. The effectiveness of multicarrier PWM approaches is assessed using two parameters: frequency modulation ratio and amplitude modulation index [6]–[8].

The relation (2) defines the frequency ratio mf.  $m_f = \frac{f_c}{f_n}$  (2)

Where,  $f_c$  is the carrier frequency of a triangle signal  $f_m$  is the frequency of the modulating signal

The amplitude modulation index ma is defined as

$n_a = \frac{2A_m}{(m-1)A_c}$ (3)

Where, A<sub>m</sub> is the modulating signal's amplitude, A<sub>c</sub> is the carrier signal's peak amplitude,

m is the number of output levels

A. Proposed Phase Delayed Disposition PWM (PDD PWM)

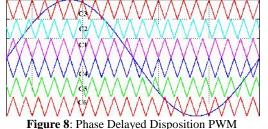

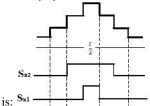

A novel PWM method called PDD PWM is employed to produce switching pulses for multilevel inverters. An n-level inverter continuously compares (n-1) carriers with the same carrier frequency ( $f_c$ ) and peak-topeak amplitude ( $A_c$ ) to a sinusoidal reference waveform with amplitude  $A_m$  and reference frequency  $f_m$ . Figure 8 illustrates how the suggested sinusoidal Phase Delayed Disposition PWM (PDD) produces seven level output voltage using six triangular carrier signals. Carrier  $C_2$  is 90<sup>0</sup> phases behind carrier  $C_1$  in PDD, while carrier  $C_3$  is 180<sup>0</sup> phases behind carrier  $C_1$  in PDD. In a similar vein, carriers  $C_5$  and  $C_6$  phase delay from carrier  $C_4$  by 90<sup>0</sup> and 180<sup>0</sup>, respectively. Six carriers that are phase delayed are distributed evenly across the sinusoidal modulating signal.

All carriers are of same frequency and same amplitude but phase delayed and level shifted compared to other. PDD is a PWM which having the characteristic of conventional phase shifted and level shifted PWM.

## B. Comparative Study with Other PWM Techniques

All of the carriers are in phase and disposed of in a continuous manner inside the bands they occupy in phase disposition (PD). Every carrier in the phase disposition method is in phase with every other carrier. In Phase Opposition Disposition (POD) modulation, all carrier waveforms above the sinusoidal zero reference are 180<sup>0</sup> out of phase with those below the zero reference. [6]. For each carrier waveform in alternate phase opposition disposition PWM (APOD), the phase shift is 180<sup>0</sup> relative to the carrier waveform next to it. The idea behind the Variable Frequency (VF) PWM approach is to use a single modulating waveform to carry many carriers at varying frequencies. Each carrier in this instance is in phase with the others, and they are arranged to occupy contiguous bands. Additionally, each carrier has a distinct frequency [6] [8] but the same amplitude. The overlapping vertical distance between each carrier in the carrier overlapping technique is half of the amplitude of one carrier amplitude. To accomplish this, arrange (n - 1) carriers so that the bands they occupy overlap one another.

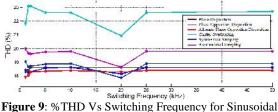

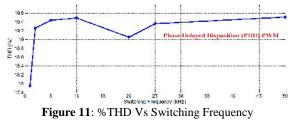

Using various typical sinusoidal PWM approaches [6][8] for different switching frequencies, Figure 9 displays the %THD. THD for switching frequencies between 1 kHz and 50 kHz using sinusoidal PWM approaches ranges from 18% to 23%.

Modulation

At 20kHz frequency %THD is reduced compared to other frequencies. This is due to the resonant condition formed by the switched capacitor with the load resistance.

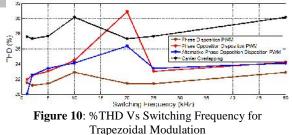

The %THD utilising various Trapezoidal PWM methods is displayed in Figure 10. These PWMs are produced in accordance with the carrier signals listed above. Phase Disposition (PD) strategies demonstrate the lowest THD for all switching frequencies by utilising trapezoidal PWM algorithms. However, in contrast to sinusoidal PWM approaches, its THD levels are considerable.

Figure 11 shows the %THD at various switching frequencies for PDD PWM technique. Compared to all other above mentioned PWM techniques PDD shows minimum %THD at 1kHz frequency. At 20kHz Switched Capacitor and load resistance forms a Resonant condition induces lower THD

So by considering %THD proposed PDD PWM at 1kHz switching frequency is selected as the optimum control technique for the Switched Capacitor Inverter.

#### C. Switching Strategy for Switched Capacitor Cell

Every quarter cycle, a switched capacitor network experiences two switching scenarios. Figure 12 illustrates how each SC cell switch switches ON at a predefined angle ( i) in the first quarter cycle and OFF at a corresponding angle (- i) in the second quarter cycle [20]. Every half cycle, these switching patterns are repeated. The SC cell's duty cycle

Figure 12: Switching Strategy for SC cell

$$D = \frac{T_{on}}{T/2}$$

Where,

$$T_{on} = ON$$

duration of Switch

T = Time period of Switching Pulse

The "FIRST ON LAST OFF" (FOLO) principle governs the switching pulses for the switched capacitor network (Sa1 & Sa2). This is because the first SC cell to turn ON will also be the last to turn OFF. And the last SC cell to turn ON will be the first to turn OFF [20].

#### V. SIMULATION ANALYSIS AND RESULTS

The SC seven level inverter was simulated using Matlab Ra2014a with an input of 5V, a switching frequency of 1kHz for fc, and a reference frequency of 50Hz for fm.

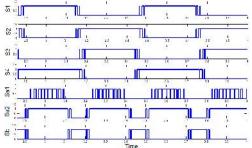

## A. Gate Pulse Generation

Gate signals are obtained by comparing a sinusoidal reference or modulating signal at the fundamental frequency (50 Hz) with a triangular carrier signal, which is at a higher frequency. In this case, a switching frequency of 1 kHz or a carrier to fundamental frequency ratio of 20 is chosen for improved performance. Seven switching pulses utilizing the PDD PWM method are depicted in Figure 13.

Figure 13: Switching Pulses using PDD techniques

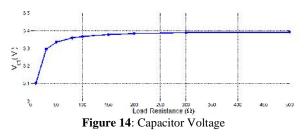

## B. Capacitor Voltage

It is important to choose a capacitor that can sustain the input voltage at the source. For low power applications, SC MLI is designed here. When  $S_{ai}$  is turned on, forward biased diodes allow capacitor  $C_i$  (i = 1,2...,N) to begin charging to a voltage equal to  $(V_{dc}-2V_f)$ . With a common switch  $S_b$ , two identical charging routes for each of the seven level inverter circuits ran in parallel to the DC input source. Each capacitor in a parallel connection has an equal charge. As seen in figure 14, the capacitor in this work is charged to 3.4V with  $V_{dc} = 5V$  and Forward diode drop of  $V_f = 0.8V$ .

#### C. Capacitor Voltage Ripple

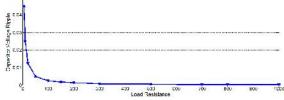

Fig. 15 displays the ripple in capacitor voltage variation with load resistance. Based on the plot, a ripple with a minimum value of 100 can be produced with a percentage less than 10%. When a load resistance greater than 100 is employed, the ripple in the capacitor will decrease correspondingly.

Figure 15: Capacitor Voltage Ripple Vs Load Resistance

#### D. Load Voltage and current

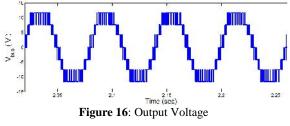

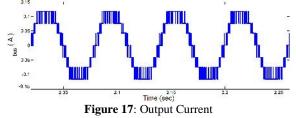

The load voltage of the seven-level topology is split into three stages. Since the load is linked across the input source and complete bridge switches are triggered, the input voltage must be determined first. The voltage at the subsequent stage is equal to the sum of the input voltage and the capacitor voltage. In a similar manner, the load voltage of the last level is equal to the total of the input and the voltages of all the series-connected capacitors. The seven-level voltage using the PDD PWM approach is shown in Figure 16. The maximum output voltage that may be achieved is 11.8V since the capacitor charges to 3.4V when fed a 5V DC input source.

Figure 17 shows the Seven level output current of the inverter with 100 resistance.

# E. Variation of Output Voltage and THD with same input

The output voltage and percentage THD for various level inverters with the same input voltage ( $V_{dc} = 5V$ ) are displayed in Table 7.2. Output levels rise and %THD falls as the number of cells decreases. Table 2 makes it evident

that the suggested inverter produces increased output for a lower DC input.

| Input Voltage = 5V |              |                        |                 |  |  |  |

|--------------------|--------------|------------------------|-----------------|--|--|--|

| No of<br>Cells     | No of Levels | Maxi Output<br>Voltage | %THD at<br>lkHz |  |  |  |

| 0                  | 3            | 4.2                    | 51.74           |  |  |  |

| 1                  | 5            | 8.36                   | 28.49           |  |  |  |

| 2                  | 7            | 11.7                   | 17.9            |  |  |  |

| 3                  | 9            | 14.87                  | 13.71           |  |  |  |

| 4                  | 11           | 17.8                   | 11.74           |  |  |  |

Table 2: Variation of parameters for the same input

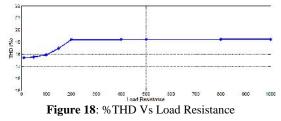

## F. Total Harmonic Distortion

The relationship between THD and load resistance is seen in Figure 18. The output's THD may change in response to changes in load resistance. The investigation shows that the THD became constant and independent of load resistance when resistance greater than 200 was applied.

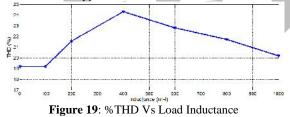

The fluctuation of THD with inductance is depicted in Figure 19. For this variant, the load inductance is changed while the load resistance is fixed at 100

#### G. Amplitude Modulation Index

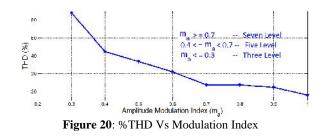

The Modulation Index is adjusted between 0 and 1 based on the modulating signal Am's amplitude measurement. The control method used in this study is set up to adjust the modulation index of the circuit depicted in figure 3 in order to generate three, five, and seven level inverter outputs.

Seven level output when ma 0.7

Five level output when  $0.4 < m_a = 0.7$

Three level output when ma 0.3

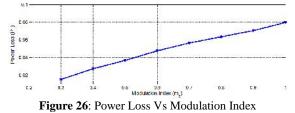

Thus, the value of the Modulation Index influences THD. The fluctuation of %THD with modulation index is displayed in Figure 20. THD significantly drops as the number of levels rises with an increase in modulation index up to 1.

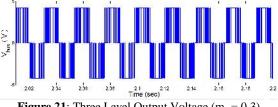

Three level inverter is a full bridge with V<sub>dc</sub> as the maximum level by taking modulation index  $m_a = 0.3$ shown in figure 21.

**Figure 21**: Three Level Output Voltage ( $m_a = 0.3$ )

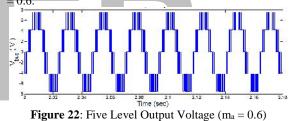

In contrast, as seen in figure 22, a five-level inverter was created by joining a single switched capacitor cell to the entire bridge network, with  $(V_{dc}+V_{c1})$  serving as the maximum voltage level and a modulation index of ma = 0.6

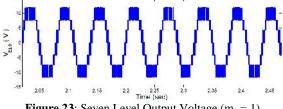

Figure 23 illustrates the seven levels achieved by cascading two switched capacitor cells in parallel to the full bridge inverter, with the maximum voltage level being  $(V_{dc}+V_{c1}+V_{c2})$  and a modulation index of  $m_a = 1$ .

**Figure 23**: Seven Level Output Voltage  $(m_a = 1)$

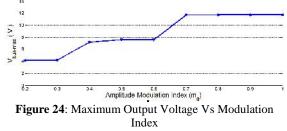

As more SC cells are added, the modulation index rises in conjunction, increasing the maximum output voltage and resulting in a variation in the number of levels. The fluctuation of the maximum output voltage with the modulation index is depicted in Figure 24. At the unity modulation index, the maximum output voltage and the lowest harmonic distortion are attained.

#### H. Frequency Modulation Index

The fluctuation of %THD with frequency modulation index mf is displayed in Table 3. At a frequency of 1 kHz or a frequency modulation index of 20, the minimum THD occurs. The ideal frequency for the seven level PDD inverter that is being proposed is 1 kHz.

Table 3: Variation of % THD with Frequency Modulation

Index

| Index                                           |                                    |                                     |  |  |  |

|-------------------------------------------------|------------------------------------|-------------------------------------|--|--|--|

| Frequency<br>Modulation Index<br>m <sub>f</sub> | Switching<br>Frequency f,<br>(kHz) | %Total Harmonic<br>Distortion (THD) |  |  |  |

| 20                                              | 1                                  | 17.95                               |  |  |  |

| 40                                              | 2                                  | 19.26                               |  |  |  |

| 100                                             | 5                                  | 19.44                               |  |  |  |

| 200                                             | 10                                 | 19.49                               |  |  |  |

| 400                                             | 20                                 | 19.05                               |  |  |  |

| 500                                             | 25                                 | 19.36                               |  |  |  |

| 1000                                            | 50                                 | 19.51                               |  |  |  |

|                                                 |                                    |                                     |  |  |  |

#### I. Power Factor

It is equal to the cosine of the output voltage to current phase difference. Additionally, active power is the portion of total power (apparent power) that is used to perform useful labour. Current lags voltage for RL loads. Power factor is 0.9656 for the minimal load inductance of 1 mH and 0.9362 for the simulated value of 100 mH, as indicated in figure 25, with the same load resistance of 100 .

Figure 25: Power Factor Vs Load Inductance

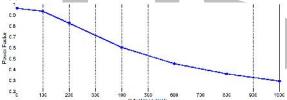

The circuit illustrated in Figure 2 is made up solely of semiconductor switches, and the power loss that results from these switching losses is on the order of mill watts (mW). The circuit is configured as a 3-level inverter for 0.3 modulation index, with four H-bridge switches conducting and 15.41 mW of switching losses across these four switches. The modulation index circuit functions as a 5-level inverter with six switches active between 0.4 and 0.6. Similarly, when all 7 switches are in operation, a 0.7 to 1 modulation index 7-level output is created. Figure 26 illustrates how power loss increases as the modulation index rises. Because output voltage increases with increasing modulation index, output power also increases.

#### K. FFT Spectrum

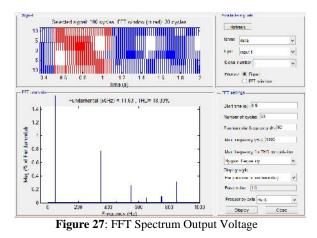

With a modulation index of ma = 1, Figure 27 displays the output voltage's FFT spectrum utilizing the Phase Delayed Disposition PWM approach. In this case, 30 cycles of output voltage with a 50Hz fundamental frequency are taken into account for calculating %THD.

#### L. Crest Factor

The instantaneous peak amplitude of a waveform divided by its root mean square value is known as the crest factor. The crest factor of the SC inverter for various modulation indices is displayed in Table 4.

| Level   | Modulation<br>Index | Crest Factor |

|---------|---------------------|--------------|

| vel     | 1                   | 1.399        |

|         | 0.9                 | 1.546        |

| 7 Leve  | 0.8                 | 1.7414       |

|         | 0.7                 | 1.99         |

| e       | 0.6                 | 1.5476       |

| 5 Leve  | 0.5                 | 1.667        |

| 5       | 0.4                 | 1.9845       |

| 3 Level | 0.3                 | 1.3258       |

The crest factor of a sinusoidal current waveform, equivalent to the current drawn by a pure resistive load, is 1.414. A genuine sinusoidal peak is 1.414 times the RMS value. According to Table 1, when Ma = 1, the crest factor is closer to the necessary value.

#### VI. COMPARATIVE STUDY

This chapter includes the comparative study of some multilevel inverter on the basis of number of components required [25]-[30].

The number of components needed to produce a single phase, seven-level output voltage waveform is shown in Table 5. Packed U Cell (PUC), one of these inverter topologies, requires less components to produce a 7-level output from a 5-level Packed U-Cell inverter [25][26][27]. However, no increased output is produced, and the capacitor must be charged to the necessary amount using a complicated capacitor balancing procedure.

## Table 5: Components count for Single Phase 7-level Inverter

| Inverter<br>Type                        | DC<br>Source<br>Voc | Capacit<br>or | Diode | Active<br>Switch | Control<br>Circuit         | Capacitor<br>Balancing | Output<br>Voltage<br>Level | Step-Up<br>Voltage |

|-----------------------------------------|---------------------|---------------|-------|------------------|----------------------------|------------------------|----------------------------|--------------------|

| CHB[1][2]                               | 3                   | 2             | 0     | 12               | Low                        | Firy                   | 3V de                      | Y                  |

| NPC[1][2]                               | 1                   | 6             | 10    | 12               | High                       | Complex                | V.12                       | No                 |

| FC[1][2]                                | 1                   | 7             | n     | 12               | High                       | Complex                | Vdc/7                      | No                 |

| PUC7<br>[25][26]                        | 1                   | 1             | 0     | 5                | High                       | Difficult              | Vac                        | No                 |

| Hybrid<br>Seven Level<br>[28]           | 1                   | 3             | 4     | 8                | Illgh                      | Difficult              | V.                         | No                 |

| C-Type [29]<br>Step-Up<br>Inverter [30] |                     | ***           |       |                  | el not poss<br>el not poss |                        |                            |                    |

| Basic SC 7<br>Level [3] [8]             | 1                   | 2             | 0     | 10               | Low                        | Eusy                   | 3V <sub>dt</sub>           | Yes                |

| Modified SC<br>/ Level [4]              | 1                   | 2             | 2     | 8                | low                        | Easy                   | 3V <sub>dc</sub>           | Yes                |

| Proposed SC<br>7 Level (10)             | 1                   | >             | 4     | 7                | how                        | Firsy                  | RV <sub>de</sub>           | Y                  |

Compared to previous inverter topologies, the proposed switched capacitor inverter may provide boosted output from a small DC input and employs fewer switching components than other boosted inverters.

Table 6: Components count for Single Phase n-level

Inverter

| Inverter Type  | DC Source     | Capacitor             | Diode        | Active Switch |   |

|----------------|---------------|-----------------------|--------------|---------------|---|

| СНВ            | $\frac{n}{2}$ | $\frac{n}{2}$         | 0            | 2(n - 1)      |   |

| NPC            | 1             | n 1                   | 2(n-2)       | 2(n-1)        | 1 |

| rc             | 1             | n                     | 0            | 2(n-1)        | 1 |

| PUC)           | 1             | $\sqrt{n.1}$ 1        | 0            | 2√n 1 2       |   |

| Hybrid MLI     | 1             | <u>n. 1</u>           | n - 3        | <b>n + 1</b>  |   |

| Е Туре МШ      | <u>n 1</u>    | 2<br>0                | 5(n - 1)     | 5(n - 1)      |   |

| Slep Uploveder | 3             | <u>n 1</u>            | <u>n 1</u>   | n 1 7         |   |

| Bassic SCM11   | 1             | <u>n 3</u>            | 2            | 3n 1          |   |

| Modified SCMU  | 1             | <u>n 3</u>            | <u>n 3</u>   | n+1           |   |

| Proposed SCML  | 1             | <u>n<sup>2</sup>3</u> | $n^{2}_{-3}$ | <u>n 1 7</u>  |   |

Table 6 is describes the number of components count for generalized structure having n-number of levels in the output. The minimum value that can substitute for n in the above table is 3.

Table 7: Components count for N module Single Phase

Inverter

| Inverter                              |           |           |           |               |                              |  |  |

|---------------------------------------|-----------|-----------|-----------|---------------|------------------------------|--|--|

| Inverter Type                         | DC Source | Capacitor | Diode     | Active Switch | Possible<br>Output<br>Levels |  |  |

| CHB                                   | N         | N         | U         | 1N            | 2N+1                         |  |  |

| NPC<br>(N=1,3,5)                      | 1         | N+1       | 2N        | 2N+2          | N+2                          |  |  |

| FC[N=1,3.5)                           | 1         | N+2       | 0         | 2N+2          | N+2                          |  |  |

| PUC<br>(Cascading<br>PUC5) [27]       | N         | N         | U         | GN            | 1N+1                         |  |  |

| PUC<br>(Cascading U<br>Cell) [25][25] | 1         | N         | U         | 2N+4          | (N+1) <sup>2</sup> +1        |  |  |

| Hybrid MLI                            | -         | NII       | 2N        | NI6           | 2N ( )                       |  |  |

| F Type MH<br>Step Up<br>Inverter      | 4N<br>1   | 0<br>2N   | 10N<br>2N | 10N<br>2N+4   | 12N+1<br>4N+1                |  |  |

| Dasic SCMLI                           | 1         | N         | 0         | DIN 14        | 2N I 3                       |  |  |

| Modified SC<br>MIT                    | 1         | N         | N         | 2N (4         | 2N ( )                       |  |  |

| Proposed<br>SCMLI                     | 1         | N         | 2N        | N+5           | 2N+3                         |  |  |

Table 7 shows number of DC source Capacitors, Diodes,

Number of levels and semiconductor switches are determined by the number of units (N). There are two ways to cascade a packed U-cell inverter: (i) Packed U-Cell cascade [27] (ii) a single U-Cell cascaded. The alternative approach is to construct different levels utilising DC linkages, therefore it would have levels like 5, 10, 17, 26 [25]. The first method generates 5, 9, 13 levels [27]. The minimum level produced by the E-Type inverter [29] from a single module unit is 13, and the minimum level produced by the step-up inverter [30] is 5. For traditional Neutral Clamped and Flying Capacitor inverters, the number of module units can be changed in steps of 1, 3, 5, etc.

## VII. EXPERIMENTAL SETUP AND RESULTS

Figure 28: Experimental Setup of the Proposed Seven Level Inverter

The hardware setup for the seven-level inverter with switched capacitors is shown in Figure 28.

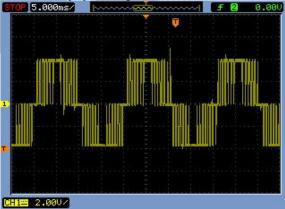

The PIC16F877A microcontroller uses the Phase Delayed Disposition PWM (PDD) approach to create pulses that control the MOSFET (IRF540). PDD provides a lower percentage of total harmonic distortion (THD) across all switching frequencies. With the help of an optocoupler TLP250 Driver/Optocoupler IC, these control pulses are amplified. The three-level voltage with ma= 0.3 is displayed in Figure 29.

Figure 29: Experimental Result of Three Level Inverter

Figure 30 shows the five level voltage of the proposed topology with  $m_a$ = 0.6.

Figure 30: Experimental Result of Five Level Inverter

Figure 31 shows the seven level voltage of the proposed topology with  $m_{a}\!\!=\!1.$

Figure 31: Experimental Result of Seven Level Inverter

#### **VIII.CONCLUSIONS**

This study examines the impact of modulation index on a step-up SC seven-level inverter, which combines a complete bridge inverter with a DC-DC converter. There are many cascaded switched capacitor cells in a DC-DC converter. Comparing this multilayer inverter to switched capacitor multilevel inverters and regular inverters, you can see that it requires a very small number of switching components. A streamlined process for creating simulation models for multicarrier PWM methods using different modulating and carrier signals is demonstrated. Out of all the multicarrier PWM approaches, Phase Delayed Disposition (PDD) PWM delivers the least amount of THD. Operation and performance analysis of SC inverters is investigated based on seven-level prototype. It is possible to reach levels three, five, and seven by managing the modulation index varying from 0.3 to 1. An output level with the largest amplitude and the lowest percentage of overall harmonic distortion are produced by a control strategy with a unity modulation index. Additionally, under unity modulation index PWM control, the crest factor improves.

#### REFERENCES

- Akira Nabae, Isao Takashi, "A New Neutral-Point-Clamped PWM Inverter", *IEEE transaction on industrial* applications, Vol. IA-17, No. 5. September/October 1981.

- [2]. J. Rodriguez, Jih-Sheng Lai and Fang Zheng Peng, "Multilevel inverters: a survey of topologies, controls, and applications," in *IEEE Transactions on Industrial Electronics*, vol. 49, no. 4, pp. 724-738, Aug. 2002, doi: 10.1109/TIE.2002.801052.

- [3]. S. S. Deshmukh and H. T. Jadhav, "Effective loss reduction analysis in new switched-capacitor boost-multilevel inverter using series/parallel conversion," 2014 IEEE Students' Conference on Electrical, Electronics and Computer Science, Bhopal, India, 2014, pp. 1-5, doi: 10.1109/SCEECS.2014.6804460.

- [4]. E. Zamiri, N. Vosoughi, S. H. Hosseini, R. Barzegarkhoo and M. Sabahi, "A New Cascaded Switched-Capacitor Multilevel Inverter Based on Improved Series–Parallel Conversion With Less Number of Components," in *IEEE Transactions on Industrial Electronics*, vol. 63, no. 6, pp. 3582-3594, June 2016, doi: 10.1109/TIE.2016.2529563.

- [5]. B. Karami, R. Barzegarkhoo, A. Abrishamifar and M. Samizadeh, "A switched-capacitor multilevel inverter for high AC power systems with reduced ripple loss using SPWM technique," *The 6th Power Electronics, Drive Systems & Technologies Conference (PEDSTC2015)*, Tehran, Iran, 2015, pp. 627-632, doi: 10.1109/PEDSTC.2015.7093347.

- [6]. T. Sengolrajan, B. Shanthi, S. P. Natarajan, "Comparative Study of Multicarrier PWM Techniques for Seven Level Cascaded Z-Source Inverter", *International Journal of Computer Applications (Cat. No.01CH37181), (0975 8887)* Volume 65 No.6, March 2013.

- [7]. J. A. Starzyk, Ying-Wei Jan and Fengjing Qiu, "A DC-DC charge pump design based on voltage doublers," in *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 48, no. 3, pp. 350-359, March 2001, doi: 10.1109/81.915390.

- [8]. M.Kanimozhi, P Geetha, "A New Boost Switched Capacitor Multilevel Inverter Using Different Multi Carrier PWM Techniques", 2014 International Conference on Circuit, Power and Computing Technologies [ICCPCT], 978-1-4799-2397-7/14, IEEE 2014.

- [9]. Amrita Mariam Varghese, Beena M Varghese, Elizabeth Sebastian, "FPGA based Single Phase Switched Capacitor Boost Multilevel Inverter", APEC 2001. *IJSRD-International Journal for Scienti\_c Research and Development*, Vol. 3, Issue 07, 2015 | ISSN (online): 2321-0613.

- [10]. Yuanmao Ye, K.W.E. Cheng, Junfeng Liu, and Kai Ding, "A Step-Up Switched- Capacitor Multilevel Inverter with Self Voltage Balancing", APEC 2001. *IEEE Transactions* On Industrial Electronics, 10.1109/TIE.2014.2314052, 2013.

- [11]. N. A. Rahim, M. F. M. Elias and W. P. Hew, "Transistor-Clamped H-Bridge Based Cascaded Multilevel Inverter With New Method of Capacitor Voltage Balancing," in *IEEE Transactions on Industrial Electronics*, vol. 60, no. 8, pp. 2943-2956, Aug. 2013, doi: 10.1109/TIE.2012.2200213.

- [12]. P. Thongprasri, "A 5-Level Three-Phase Cascaded Hybrid Multilevel Inverter", *International Journal of Computer* and Electrical Engineering, Vol. 3, No 6, December 2011.

[13]. Y. Hinago and H. Koizumi, "A switched-capacitor inverter

- [13]. Y. Hinago and H. Koizumi, "A switched-capacitor inverter using series/ parallel conversion", Proc. *IEEE Int. Symp. Circuits, Syst* 2010, pp. 31883191.

- [14]. B. Axelrod, Y. Berkovich and A. Ioinovici, "A cascade boost-switched-capacitor-converter - two level inverter with an optimized multilevel output waveform," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 52, no. 12, pp. 2763-2770, Dec. 2005, doi: 10.1109/TCSI.2005.852205.

- [15]. R. Bensraj, S. P. Natarajan' "Multicarrier Trapezoidal Pwm Strategies Based On Control Freedom Degree For MSMI", ARPN Journal of Engineering and Applied Sciences, Vol. 5, No. 5, May 2010.

- [16]. Rekha Agrawal, Jitendra Kumar Tandekar, "Multi-Carrier Pulse Width Modulation Schemes for Multilevel Converters", 2016 IEEE Students' Conference on Electrical, Electronics and Computer Science.

- [17]. K. Gopalakrishnan, M. Sundar Raj, "Harmonic Evaluation of Multicarrier Pwm Techniques for Cascaded Multilevel Inverter", *Middle-East Journal of Scientific Research 20* (7): 819-824, 2014.

- [18]. Brendan Peter McGrath, "Multicarrier PWM Strategies for Multilevel Inverters", *IEEE Transactions on Industrial Electronics*, VOL. 49, NO. 4, AUGUST 2002

- [19]. Shahab Yousefizad, Vahab Yousefizad, Vahid Eslampanah, Hamid Abbasi, "THD Minimisation for Phase Voltage of Multilevel Inverters Using Genetic Algorithm", *The International Journal Of Engineering And Science* (*IJES*), Volume 4, Issue 2.

- [20]. A. Gholizad and M. Farsadi, "A Novel State-of-Charge Balancing Method Using Improved Staircase Modulation of Multilevel Inverters," in *IEEE Transactions on Industrial Electronics*, vol. 63, no. 10, pp. 6107-6114, Oct. 2016, doi: 10.1109/TIE.2016.2580518.

- [21]. Muhammad H Rashid, "Power Electronics Handbook: Devices, Circuits, and Applications", *Second Edition, Academic Press.*

- [22]. Dr. P S Bimbhra, "Power Electronics", Khanna Publishers, Delhi, 2012

- [23]. Ned Mohan, Tore M. Undeland, William P. Robbins, 'Power Electronics', John Wiley & Sons Publications, 3rd edition, 2006.

- [24]. Y. Ounejjar, K. Al-Haddad and L. -A. Gregoire, "Packed U Cells Multilevel Converter Topology: Theoretical Study and Experimental Validation," in *IEEE Transactions on Industrial Electronics*, vol. 58, no. 4, pp. 1294-1306, April 2011, doi: 10.1109/TIE.2010.2050412.

- [25]. H. Vahedi, P. -A. Labbé and K. Al-Haddad, "Sensor-Less Five-Level Packed U-Cell (PUC5) Inverter Operating in Stand-Alone and Grid-Connected Modes," in *IEEE Transactions on Industrial Informatics*, vol. 12, no. 1, pp. 361-370, Feb. 2016, doi: 10.1109/TII.2015.2491260.

- [26]. H. Vahedi and K. Al-Haddad, "Real-Time Implementation of a Seven-Level Packed U-Cell Inverter with a Low-Switching-Frequency Voltage Regulator," in *IEEE Transactions on Power Electronics*, vol. 31, no. 8, pp. 5967-5973, Aug. 2016, doi: 10.1109/TPEL.2015.2490221.

- [27]. Ajesh P S, Beena M Varghese, Annie P Oommen "Performance Analysis of Cascadable U-Cell Multi Level Inverter", 2017 IEEE International Conference on Technological Advancements in Power and Energy (TAP Energy 2017)

- [28]. C. -H. Hsieh, T. -J. Liang, S. -M. Chen and S. -W. Tsai, "Design and Implementation of a Novel Multilevel DC– AC Inverter," in *IEEE Transactions on Industry Applications*, vol. 52, no. 3, pp. 2436-2443, May-June 2016, doi: 10.1109/TIA.2016.2527622.

- [29]. Emad Samadaei, S.A. Gholamian, A. Sheikholeslami, J. Adabi, "An Envolope Type Module Asymetric Multilevel inverters with Reduced Components", *IEEE Transactions* On Industrial Electronics, 2016

- [30]. F. Gao, "An Enhanced Single-Phase Step-Up Five-Level Inverter," in *IEEE Transactions on Power Electronics*, vol. 31, no. 12, pp. 8024-8030, Dec. 2016, doi: 10.1109/TPEL.2016.2555934.

## About Authors

Bhagyalakshmi P S pursued the B. Tech degree in Electrical Engineering from Mar Athanasius College of Engineering, Kothamangalam under Mahatma Gandhi University Kerala, India in 2014. She is currently pursuing M. Tech degree in power electronics. Published three Papers in International Journals conferences. The main areas of interests are power electronics and power system

**Beena M Varghese** pursued B. Tech and ME degree from MG University, Kottayam in 1992 and PSG Coimbatore in 2003 respectively. She is currently working as a faculty in Electrical Department, MA College of Engineering, Kothamangalam. Her research interest includes control system, power electronics and drives.

**Dr. Bos Mathew Jos** pursued B. Tech and M. Tech degrees from MG University, Kottayam in 1993 and NIT Trichy in 2004 respectively. Received ph. D. in power electronics and drives from NIT Trichy. He is currently working as a faculty in Electrical Department, MA College of Engineering, Kothamangalam. His research interest includes power system, Drives and control.